Intel Foundry vừa đánh dấu cột mốc quan trọng trong kỷ nguyên sản xuất bán dẫn với việc hoàn thiện máy quang khắc siêu cực tím (Extreme Ultraviolet, viết tắt EUV) sử dụng công nghệ khẩu độ số học lớn (High Numerical Aperture, viết tắt High NA) thương mại đầu tiên trong ngành bán dẫn, được đặt tại nhà máy của Intel ở Hillsboro, Oregon.

Được phát triển bởi ASML, công ty hàng đầu thế giới về sản xuất thiết bị quang khắc.Hệ thống TWINSCAN EXE:5000 High NA EUV của Intel hiện đang trong quá trình hiệu chuẩn để sẵn sàng cho lộ trình sản xuất sắp tới của hãng. Điểm nổi bật của hệ thống nằm ở khả năng cải tiến vượt bậc về độ phân giải và khả năng thu nhỏ các chi tiết trên những thế hệ vi xử lý tiếp theo nhờ thiết kế quang học tiên tiến cho việc in bản mạch lên các tấm bán dẫn silicon (wafer) trở nên chính xác hơn, làm tiền đề cho sự ra đời của những bộ vi xử lý thế hệ mới mạnh mẽ hơn.

Các nhà sản xuất chip phụ thuộc vào việc thu nhỏ – làm cho transistor nhỏ hơn và đóng gói nhiều hơn chúng vào các wafer silic – để thúc đẩy tiến bộ trong công nghệ vi mạch. Đây không phải là cách duy nhất để cải thiện chip; kiến trúc mới, ví dụ, cũng có thể tăng hiệu suất. Nhưng có một lý do khiến Luật Moore về cơ bản là quy luật của đất nước: Việc thu nhỏ đã đứng sau sự tăng trưởng mũi nhọn về sức mạnh tính toán trong hơn 50 năm qua.

Trong nhiều năm, các nhà khoa học đã đẩy công nghệ phôi siêu cực tím sâu (DUV) tới giới hạn của nó. Để giảm kích thước của đặc tính nhỏ nhất có thể được in ra, được biết đến là kích thước quyết định (CD), có hai nút chính chúng ta có thể điều chỉnh: bước sóng của ánh sáng, λ, và aperture số, NA. Tuy nhiên, bây giờ, không còn nhiều không gian để điều chỉnh những nút đó trong các hệ thống DUV của chúng ta.

Phôi siêu cực tím (EUV) cho phép chúng ta điều chỉnh nút bước sóng một cách lớn: Nó sử dụng ánh sáng 13,5 nm, so với 193 nm cho các hệ thống DUV có độ phân giải cao nhất. Khi nền tảng phôi EUV tiền sản xuất đầu tiên của chúng tôi, NXE, được vận chuyển lần đầu tiên vào năm 2010, nó đã mang lại sự giảm CD từ hơn 30 nm trong DUV xuống còn 13 nm với EUV.

High NA EUV lithography là gì?

High NA EUV là bước tiến tiếp theo trong nỗ lực không ngừng của các nhà khoa học tại ASML để thu nhỏ. Tương tự như các hệ thống NXE, nó sử dụng ánh sáng EUV để in các đặc điểm nhỏ trên wafer silic. Và bằng cách điều chỉnh nút NA, họ mang lại độ phân giải tốt hơn: Nền tảng mới, được biết đến với tên gọi EXE, cung cấp cho các nhà sản xuất chip một CD là 8 nm. Điều đó có nghĩa là có thể in transistor nhỏ hơn 1,7 lần – và do đó đạt được mật độ transistor cao hơn 2,9 lần – so với các hệ thống NXE.

1. Kính quang lớn hơn, dạng hình mờ để hình ảnh sắc nét hơn

Tiến bộ nổi bật trong High NA EUV lithography là các kính quang mới. ‘NA’ trong tên chỉ số này đề cập đến khẩu độ số – một chỉ số đo khả năng của hệ thống quang học để thu thập và tập trung ánh sáng. Và nó được gọi là High NA EUV vì chúng tôi đã tăng NA từ 0.33 trong các hệ thống NXE của chúng tôi lên 0.55 trong các hệ thống EXE. NA cao hơn là điều làm cho các hệ thống này có độ phân giải tốt hơn.

Việc triển khai việc tăng NA này có nghĩa là sử dụng các gương lớn hơn. Nhưng các gương lớn hơn tăng góc mà ánh sáng đập vào bản sao, nơi có mẫu cần được in. Ở góc lớn hơn, bản sao mất khả năng phản xạ, vì vậy mẫu không thể được chuyển sang wafer. Vấn đề này có thể đã được giải quyết bằng cách co giãn mẫu 8 lần thay vì 4 lần như trong các hệ thống NXE, nhưng điều đó sẽ yêu cầu các nhà sản xuất chip chuyển sang sử dụng các bản sao lớn hơn.

Thay vào đó, EXE sử dụng một thiết kế tài tình: kính quang dạng hình mờ. Thay vì đồng đều co giãn mẫu đang được in, các gương của hệ thống giảm mẫu 4 lần ở một hướng và 8 lần ở hướng khác. Giải pháp này giảm góc mà ánh sáng đập vào bản sao và tránh được vấn đề phản xạ. Quan trọng hơn, nó cũng giảm thiểu tác động của công nghệ mới này đối với hệ sinh thái bán dẫn bằng cách cho phép các nhà sản xuất chip tiếp tục sử dụng các bản sao có kích thước truyền thống.

2. Các giai đoạn nhanh hơn để tăng năng suất

Do các kính quang dạng hình mờ của nó, các hệ thống EXE có các lĩnh vực chiếu rộng gấp đôi so với các thế hệ NXE trước đó. Do đó, cần phải chiếu gấp đôi lần để tạo ra một wafer duy nhất.

Việc cần phải chiếu gấp đôi có thể đã có nghĩa là mất gấp đôi thời gian để in một wafer. Thay vào đó, chúng tôi đã coi đó là một thách thức. Giải pháp? Các giai đoạn wafer và reticle nhanh hơn nhiều. Giai đoạn wafer trong hệ thống EXE tăng tốc lên 8g, gấp đôi tốc độ so với giai đoạn wafer của NXE. Và giai đoạn reticle của EXE tăng tốc nhanh hơn bốn lần so với của NXE – 32g, tương đương với một chiếc xe đua tăng tốc từ 0 đến 100 km/h trong 0.09 giây.

Với các giai đoạn mới của nó, TWINSCAN EXE:5000 có thể in hơn 185 wafers mỗi giờ, một mức tăng so với các hệ thống NXE đã được sử dụng trong sản xuất hàng loạt lớn. Và chúng tôi có một lộ trình để tăng số wafers in lên 220 wafers mỗi giờ vào năm 2025. Năng suất này là yếu tố quan trọng để đảm bảo việc tích hợp High NA vào các nhà máy chip là kinh tế cho các nhà sản xuất chip.

3. Quy trình sản xuất đơn giản hóa để hiệu quả chi phí

High NA EUV lithography sẽ cho phép các nhà sản xuất chip in các đặc điểm nhỏ nhất trên các vi mạch tiên tiến nhất. Nhưng trong thời gian chờ đợi đó, các nhà sản xuất chip không chỉ đứng yên đợi. Họ đã tìm ra các cách khác để vượt qua các giới hạn về độ phân giải của các hệ thống lithography của họ bằng cách sử dụng các quy trình sản xuất phức tạp hơn.

Những biện pháp tạm thời này đi kèm với một chi phí. Chúng tăng thời gian sản xuất và tạo ra cơ hội bổ sung để giới thiệu các khuyết điểm có thể ảnh hưởng đến hiệu suất của vi mạch. Với CD của mình là 8 nm, EXE:5000 cho phép các nhà sản xuất chip đơn giản hóa quy trình sản xuất của họ. Kết quả? Sản xuất vi mạch tiên tiến hiệu quả chi phí hơn.

4. Chung và linh hoạt để cải thiện hiệu suất

EXE:5000 đại diện cho sự tiến hóa của công nghệ EUV lithography, không phải là một cách cách mạng. Chúng tôi đã tái sử dụng nhiều công nghệ EUV hiện có của chúng tôi nhất có thể và chỉ thay đổi những khía cạnh cần thiết để mang lại sự cải thiện về độ phân giải và năng suất của hệ thống. Và, giống như các hệ thống NXE EUV của chúng tôi, các hệ thống EXE được tạo thành từ các mô-đun có thể được kiểm tra độc lập trước khi được tích hợp vào một hệ thống hoàn chỉnh.

Tại sao chúng tôi ưu tiên sự chung và tính linh hoạt trong toàn bộ các hệ thống EUV lithography của chúng tôi? Bởi vì như vậy, tất cả các hệ thống của chúng tôi đều hưởng lợi từ những bài học hơn 20 năm phát triển EUV. Sử dụng công nghệ đã được thử nghiệm giảm thiểu rủi ro của các vấn đề phát sinh. Và các mô-đun làm giảm thiểu quá trình cài đặt và tích hợp hệ thống vào một nhà máy của khách hàng. Điều đó có nghĩa là các hệ thống sẽ bắt đầu sản xuất chip nhanh hơn – khách hàng của chúng tôi sẽ bắt đầu nghiên cứu và phát triển vào năm 2024–2025 và chuyển sang sản xuất hàng loạt vào năm 2025–2026.

Kế hoạch thời gian nhanh chóng là tin vui cho tất cả mọi người: Càng sớm các hệ thống này bắt đầu in các vi mạch tân tiến, thì công nghệ tiên tiến mà chúng cho phép sẽ sớm được sử dụng.

5. Tính năng, hiệu suất và hiệu quả năng lượng của vi mạch được cải thiện

Độ phân giải 8 nm của EXE:5000 có nghĩa là các nhà sản xuất chip có thể đóng gói nhiều transistor hơn vào một chip duy nhất. Transistor nhỏ hơn có hiệu suất năng lượng cao hơn – điều đó có nghĩa là các vi mạch sẽ có khả năng thực hiện nhiều công việc hơn với ít năng lượng hơn. Vì vậy, các đặc điểm nhỏ được in bởi EXE:5000 sẽ tạo nền tảng cho các vi mạch tiên tiến nhất. Và, nhờ vào tính năng năng suất của hệ thống, các nhà sản xuất chip có thể sản xuất các vi mạch này ở số lượng lớn.

6. Tác động của High NA EUV lithography

Sự đổi mới trong vi mạch ngày càng quan trọng trong thế giới kỹ thuật số hiện nay. Người tiêu dùng mong đợi các loại và thế hệ thiết bị điện tử mới nhỏ gọn nhưng có khả năng thực hiện nhiều công việc hơn, và làm điều đó tốt hơn và nhanh hơn. Với High NA EUV lithography, các nhà sản xuất chip có thể đáp ứng các yêu cầu của người tiêu dùng.

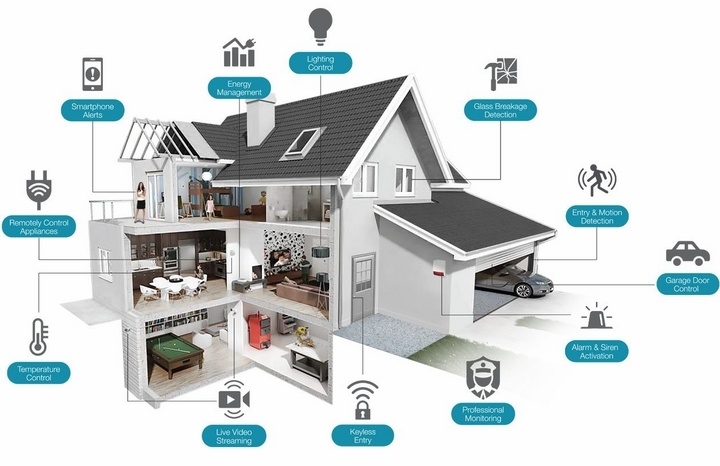

Các vi mạch đầu tiên được sản xuất bằng EXE:5000 sẽ là chip Logic node 2 nm. Các vi mạch nhớ có mật độ transistor tương tự sẽ tiếp theo. Những vi mạch này sẽ kết hợp các đặc điểm nhỏ nhất với các kiến trúc hàng đầu để cung cấp năng lượng cho công nghệ của tương lai: robot, trí tuệ nhân tạo, internet vạn vật, và xa hơn.

Mục lục nội dung

Bài viết liên quan

Tháng mười một 6, 2025